Inquire

stratix 10 emif user guide

1.1. Q - Terasic

Apollo S10 SoM. User Manual Intel Stratix 10 SoC FPGA Boot User Guide. FPGA I/O and HPS external memory interface (EMIF) I/O configuration data.

Learn More

256 10 FPGA IP User Guide - Altera · PDF fileExternal Memory

External Memory Interfaces Intel® Stratix® 10 FPGA IP User Guide Updated for Intel® Quartus® Intel Stratix 10 EMIF Architecture: Input DQS Clock Tree.

Learn More

Solved: MPFE for Stratix 10 EMIF? - Intel Communities

2022. 3. 7. · 03-07-2022 01:52 PM. For past designs, I've used the UniPHY SDRAM memory controller for a DDR memory interface. That controller contained a multi-port front end (MPFE) which could be used to create multiple smaller ports for accessing the DDR memory from user logic. I'm now working on a Stratix 10 design using the EMIF interface, and there does

Learn More

Embedded Design Handbook

Using Tightly Coupled Memory with the Nios II Processor Tutorial. The board must have either Intel MAX® 10, Stratix series,

Learn More

2.4. Stratix® 10 EMIF Architecture: Introduction

2022. 8. 24. · Differences Between User-Requested Reset in Stratix® 10 versus Arria® 10 2.13. Compiling Stratix® 10 EMIF IP with the Quartus Prime Software 2.14. Debugging Stratix® 10

Learn More

External Memory Interface Handbook Volume 2: Design

To enable the data pin inversion feature, click Configuration Register Settings > Option Control in the Arria 10 EMIF IP. QDR IV SRAM devices also have a

Learn More

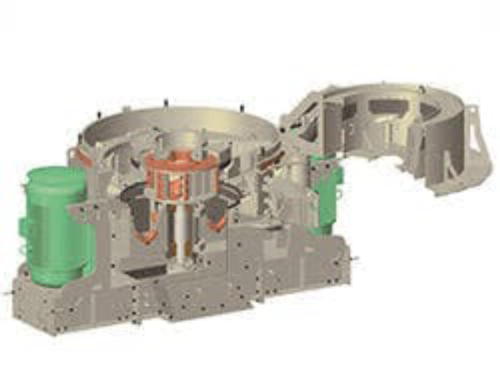

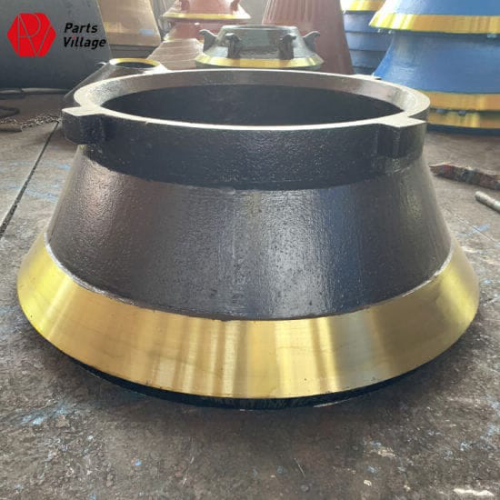

HP500 CNTRWGHT ASSY | stratix 10 emif user guide

Cone crusher main shaft Jaw crusher main shaft. Part of the rotary movement in the machine is mounted on the shaft. Usually the cone crusher or jaw crusher have a main shaft and a pinion shaft.

Learn More

PDF 256 10 FPGA IP User Guide - YIC-Electronics.comPDF

External Memory Interfaces Intel® Stratix® 10 FPGA IP User Guide Updated for Intel ® Quartus Prime Design Suite: 18.1 Subscribe Send Feedback UG-S10EMI | 2018.09.24 Latest document on the web: PDF | HTML

Learn More

Centro de soporte de IP de interfaces de memoria externa - Intel

Video tutorial de estimación de especificaciones de EMIF. Herramientas de EMIF Intel Stratix 10 device pin-out y emiF address/command pin-out

Learn More

Designed to meet the memory-intensive workload demands of networking

Designed to meet the memory-intensive workload demands of networking and data center applications, the DDR4 memory PHY delivers maximum performance and power efficiency while maintaining full compatibility with the DDR4 and DDR3 industry standards. With the Rambus DDR4 Controller it comprises a complete DDR4 memory interface subsystem.. DDR4 is full-featured, easy-to-use, synthesizable design

Learn More

External Memory Interfaces Intel Stratix 10 FPGA IP Design Example User Guide

The Intel ® Stratix® 10 EMIF IP provides external memory interface support for DDR3, DDR4, QDR II/II+/Xtreme, QDR-IV, and RLDRAM 3 memory protocols. Search Intel® FPGAs and Programmable Devices / Documentation / External Memory Interfaces Intel Stratix 10

Learn More